# Enanonewsletter

No. 17/18 • Special Issue • www.phantomsnet.net

SEMICONDUCTOR NANOWIRES Status of the field - research and applications

# CIC COOPERATIVE RESEARCH CENTER

Nanooptics

www.nanogune.eu

Nanodevices

Nanobiotechnology

Nanoscale imaging

# **Dear Readers,**

This E-nano Newsletter special double issue contains a report providing insights in a relevant field for nanoscale devices research that has developed very rapidly during the last five years: semiconductor nanowires (NW).

Nanowire-based devices offer unique opportunities in different research areas and represent a possible impact as key add-on technologies to standard semiconductor fabrication.

The nanoICT position paper provides an analysis of the current status of nanowires research and applications at the nanoscale in several areas of interest: nanowire-based electronics, fundamental studies of nanowire growth, opportunities for opto-electronic devices based on NW technology, application for Energy harvesting as implemented in solar cells and thermoelectrics and finally their use in biology and in medical applications.

We would like to thank all the authors who contributed to this issue as well as the European Commission for the financial support (project nanoICT No. 216165).

**Dr. Antonio Correia** Editor - Phantoms Foundation

# Deadline for manuscript submission

Issue No. 19: June 30, 2010 Issue No. 20: August 31, 2010

Depósito legal/Legal Deposit: M-43078-2005

Impresión/Printing: Madripapel, S.A.

### Contents

Semiconductor nanowires: Status of the field - research and applications

| 5  | Introduction                            |

|----|-----------------------------------------|

| 5  | Overview of nanowire electronics        |

| 27 | Overview of nanowire growth             |

| 30 | Overview transport / optical properties |

|    | of nanowires                            |

| 35 | Overview of nanowires for energy        |

|    | applications                            |

| 38 | Overview of nanowire for biology /      |

|    | medicine                                |

| 41 | Annex I                                 |

| 41 | 1. Report from the NODE workshop        |

|    | on nanowire electronics                 |

| 43 | 2. Report from the Nanowire growth      |

|    | workshop (NWG2009)                      |

| 47 | Annex 2                                 |

| 47 | 1. NODE project objectives and main     |

|    | achievements                            |

| 47 | 2. NODE publications                    |

| 54 | Annex 3                                 |

|    | European Nanowire-engaged groups        |

|    |                                         |

# **Editorial Information**

No. 17/18 December 2009 March 2010 Published by Phantoms Foundation (Spain)

### Editor

Dr. Antonio Correia antonio@phantomsnet.net Assistant Editors

José Luis Roldán, Maite Fernández, Conchi Narros, Carmen Chacón and Viviana Estêvão

### I500 copies of this issue have been printed. Full color newsletter available at:

www.phantomsnet/Foundation/newsletters.php For any question please contact the editor at: antonio@phantomsnet.net

### **Editorial Board**

Adriana Gil (Nanotec S.L., Spain), Christian Joachim (CEMES-CNRS, France), Ron Reifenberger (Purdue University, USA), Stephan Roche (CEA-INAC, France), Juan José Saenz (UAM, Spain), Pedro A. Serena (ICMM-CSIC, Spain), Didier Tonneau (CRMCN-CNRS, France) and Rainer Waser (Research Center Julich, Germany)

# INNOVATIVE SOLUTIONS FOR NANOFABRICATION AND SEMICONDUCTOR NAVIGATION

# Ultra high resolution electron beam lithography and nano engineering workstation

e LiNE

...Nano metrology ...Nanoscale imaging ...EDX-chemical analysis ...Electron beam etching ...Electrical and mechanical probing ...Electron Beam Induced Deposition (EBID)

# Upgrade your SEM / FIB to a nanolithography system

benefiting from a reliable modular attachment concept

ELPHY<sup>TM</sup> *PLus* The advanced lithography system.....

ELPHY<sup>™</sup> Quantum The universal lithography attachment......

Laser Interferometer Stage The ultimate positioning tool.....

NANOTECHNOLOGY

Sub 10 nm lithography

E-beam deposition

Nano Sokoban

Photonic crystal with proximity effect correction

X-ray analytics

# Semiconductor nanowires: Status of the field - research and applications

# Introduction

List of experts / Contributors: With the core of this report based on the final publishable report from the EU/IST funded NODE-project, basically all 12 partners of this program have contributed in different ways. Most significant have been the over-all coordination by C. Thelander and L. Samuelson (Lund University) and the site leaders of the 12 partners: L-F. Feiner (Philips), W. Riess (IBM), G. Curatola (NXP), L. Ledebo (QuMat), W. Weber (NamLab, previously Qimonda), J. Eymery (CEA), U. Gösele (MPI), P. Vereecken (IMEC), L. P. Kouwenhoven (TU Delft), A. Forchel (Univ. Würzburg), A. Tredicucci (SNS-Pisa). Other people that have contributed are V. Zwiller (TU Delft), J-C Harmand and P. Caroff (LPN-CNRS), J. Johansson, C. Prinz, J. Tegenfeldt, K. Deppert and H. Linke (Lund Univ.). Many others have directly and indirectly contributed to this report.

**Keywords:** Nanowire, growth, processing, physics, characterization, devices, integration, energy, biology.

### Institutions acronyms:

LU: Lund University; **PRE:** Philips Research Laboratory Eindhoven; **MPI:** Max-Planck-Institut; **IBM:** IBM Zurich; **WV:** University Wurzburg; **QM:** QuMat; **TUD:** Technical University of Delft; **NL:** NamLab, previously Qimonda; **IMEC:** Interuniversity Microelectronics Center; **SNS:** Scuola Normale Superiore di Pisa; **CEA:** Commissariat à l'Énergie Atomique; **CNRS/ IEMS:** Centre National de la Recherche Cientifique / Institut d'Electronique, de Microelectronique et de Nanotechnologie.

The field of semiconductor nanowires (NWs) has during the last five years developed very rapidly. Within the European frame-work the strongest efforts have been in the development of nanowire-based electronics, i.e. nanowire transistors, as performed in the largest Integrated Project within "Emerging Nanoelectronics", called "Nanowire-based One-Dimensional Electronics (NODE)". Considering the rather high maturity of the research field reached through NODE, we use the final publishable report as the core of this report. We also attach as an appendix a summary of impressions from the dissemination workshop that was organized at the con-

# nanoICT research

clusion of NODE, when the "NODE Workshop on Nanowire Electronics" was organized in Lund in September 2009. Here we also summarize the input and recommendations as provided by the invited experts: W. Hänsch (IBM), M. Passlack (TSMC), J. Knoch (TU Dortmund), T. Mikolajick (NAMLAB), H. de Man (IMEC), and L. Tilly (Ericsson).

Other central areas of nanowire research and applications deal with fundamental studies of nanowire growth, as very actively pursued through the arrangements of a series of four European Workshops on Growth on Nanowires, most recently the 4th arranged in Paris in October 2009. We include as an appendix a summary of the status as revealed from this workshop (written by J-C Harmand and F. Glas). Incorporated in this article is also a status of the field description provided by J. Johansson and P. Caroff.

In order to provide a more detailed description of the level of understanding and control of physical properties of nanowires, a special chapter has been provided for this by L. P. Kouwenhoven and V. Zwiller. This chapter also deals in more detail with the opportunities for opto-electronic devices based on NW technology.

Another important area of NW research relates to their application for Energy harvesting as implemented in solar cells and thermoelectrics. For the use of NWs in photovoltaics was recently started an EU-project called AMON-RA. We enclose two short descriptions of Nanowires for energy, provided by K. Deppert.

An increasingly important aspect of nanowire research deals with their use in biology and in medical applications. We include here also a description of the state of the art as provided by C. Prinz and J. Tegenfeldt. For each of these areas we try to provide some of the key references but these are far from complete lists of references.

### I. Overview of nanowire electronics<sup>1</sup>

The integrated project "NODE" developed and evaluated technologies for growth and processing of semiconductor nanowire devices for their possible impact as key add-on technologies to standard semiconductor fabrication. The partners in NODE worked on generating a deepened understanding of the physics phenomena of one-dimensional semiconductor materials and nanowire-based devices, and on developing new functionalities not found in traditional higher-dimensional device structures.

<sup>&</sup>lt;sup>1</sup> Based on the NODE project executive summary

A set of key device families based on semiconductor nanowires were studied in detail; such as tunneling devices, and field-effect transistors. Also unique opportunities that may be offered by nanowires in different areas are explored, e.g. memory applications. NODE maked a dedicated effort to evaluate the potential for integration of nanowire-specific processing methods and to assess the compatibility with requirements from conventional semiconductor processing, as well as evaluating novel architectural device concepts and their implementation scenarios. This chapter is based on the NODE project executive summary. Detailed information about objectives and main achievements of the NODE project are available in Annex 2.

### I.I. Nanowire growth

# I.I.I. General growth control

### Controlling the crystal structure of InAs nanowires (LU)

Gold-particle seeded nanowires fabricated in materials with zinc blende as the bulk crystal structure are often observed to have wurtzite crystal structure. The general trend is that thin wires are wurtzite and thick wires are zinc blende. That is, there is a cross-over diameter

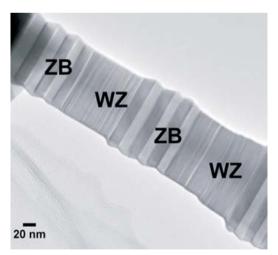

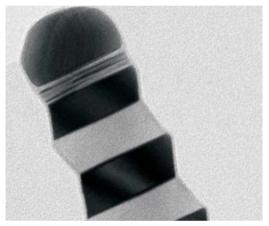

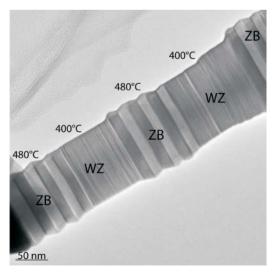

Fig 1. Polytypic superlattice, with alternating zinc blende and wurtzite structure, along an InAs nanowire.

for the preferential polytype. This cross-over diameter is temperature dependent. By carefully varying the temperature during growth we were able to fabricate superlattices with alternating zinc blende and wurtzite structure. [1]

### Crystal phase and twin superlattices (PRE)

The crystal phase of III-Vs NWs can be determined by the dopant precursor flows during growth. In InP the use of Zn-precursor favors the ZB phase, whereas the use of S-precursor favors the Wz phase. Moreover, highly regular twin superlattices can be induced in the ZB phase by tuning the Zn concentration, wire diameter and supersaturation. The effect was explained in a model based on surface energy arguments. [2]

Fig 2. TEM image of the top part of an InP NW, closely below the Au catalyst particle, showing the highly regular twin superlattice structure.

### Synergetic growth (PRE)

A counter-intuitive effect controlling the influence of wire spacing on growth rate was uncovered, synergetic

Fig 3. GaP wires next to a thick wire are taller than the second-nearest wires, which are taller than those in the middle of the field (furthest from the thick wire), showing that the growth rate of one wire is enhanced by the presence of another one and dependent on the catalytic alloy amount.

# AURIGA<sup>™</sup> Information Beyond Resolution

- Unique Imaging

- Precise Processing

- Advanced Analytics

- Future Assured

# **CrossBeam® Workstations (FIB-SEM)**

101

AURIGA

Chamber SE image of an uncoated fibre adhesive (used in modern shipbuilding). Taken with local charge compensation at 5 kV.

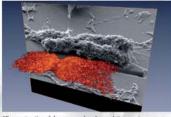

3D reconstruction of chromosomes based on real-time movie Taken with in-lens SE detector at 2 kV. Courtesy of Prof. G. Wanner, Munich, Germany.

Enabling the Nano-Age World®

Cross section through the front contact of a Si wafer-based solar cell. Taken with in-lens SE detector at 2 kV. Courtesy of Dr. F. Machalett, ersol Solar Energy AG, Erfurt, Germany.

Carl Zeiss SMT Nano Technology Systems Division info-nts@smt.zeiss.com www.smt.zeiss.com/nts

# We make it visible.

growth, which implies that at smaller spacing the competition for available material, reducing the growth rate, is counteracted by the increase in surface density of catalyst metal particles on neighboring nanowires, providing more decomposed material. [3]

# I.I.2. Heterostructures

### Epitaxial Ge/Si nanowires (MPI)

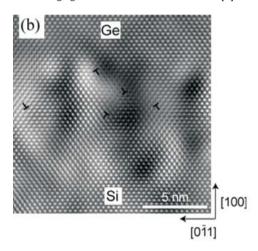

Epitaxial Ge/Si hetero-structure nanowires on Si (100) substrates were prepared in AAO templates. Usually, the Si atoms dissolved in the Au/Si eutectic catalyst act as a reservoir for Si, and the interface to Ge is smeared out. This new approach of the growth inside the AAO templates, allowed to produce a sharp interface of Ge/Si without changing the diameter of the nanowire. [4]

Fig 4. Cross-section TEM ima-ge of the Ge-Si interface.

### Morphology of axial heterostructures (LU)

An extensive investigation of the epitaxial growth of Auassisted axial heterostructure nanowires composed of group IV and III-V materials have been carried out and derived a model to explain the overall morphology of such wires. [5]

By analogy with 2D epitaxial growth, this model relates the wire morphology (i.e., whether it is kinked or straight) to the relationship of the interface energies between the two materials and the particle. This model suggests that, for any pair of materials, it should be easier to form a straight wire with one interface direction than the other, and this was demonstrated for the material combinations presented here.

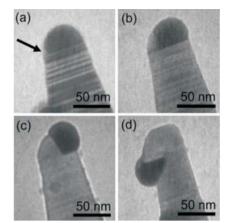

Fig 5. Images recorded during the growth of Ge on GaP nanowires by UHV-CVD.

# I.I.3. Doping

# Decoupling the radial from the axial growth rate by in situ etching (LU)

It was shown that in-situ etching can be used to decouple the axial from the radial nanowire growth mechanism, independent of other growth parameters. Thereby a wide range of growth parameters can be explored to improve the nanowire properties without concern of tapering or excess structural defects formed during radial growth. We used HCl as the etching agent during lnP nanowire growth, and etched nanowires show improved crystal quality as compared to non etched and tapered NWs. These results will make way for devices relying on doping in axial structures, where any radial overgrowth would lead to short circuiting of a device.

Fig 6. a) Tapered reference InP nanowires grown at a temperature of  $450^{\circ}$ C, b) Non tapered nanowires grown with HCl in the gas phase under otherwise identical growth conditions to a).

# P-type doping and p-n junctions in InP NWs (PRE)

Sulphur was identified as a suitable candidate for n-type doping of InP in MOVPE using  $H_2S$  as a precursor. It was

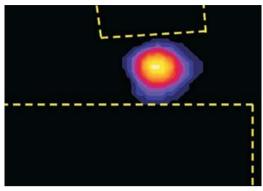

Fig 7. Optical microscope image of electroluminescent light coming from an InP NW LED, as collected by a CCD camera (the dashed lines show the positions of the electrodes).

further established that Zn-doping can be effectively used to achieve p-type doping in InP, using trimethylzinc as a precursor. The combination of S and Zn permits realization of p-n junctions in InP, showing good electrical diode characteristics in thin (20 nm-diameter) nanowires. The diodes exhibit LED behavior, testifying the high quality of the p-n junctions. [6]

### Remote p-type doping of InAs NWs (PRE)

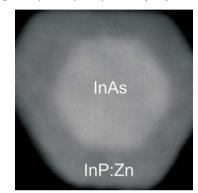

Obtaining quantitative control of doping levels in nanowires grown by the vapor-liquid-solid (VLS) mechanism is

Fig 8. Dark-field TEM image of the InAs(core)/InP:Zn(shell) NW.

# Advertisement

especially challenging for the case of p-type doping of InAs wires because of the Fermi level pinning around 0.1 eV above the conduction band. It was shown that growing a Zn-doped shell of InP epitaxially on a core InAs NW yields remote p-type doping: shielding with a p-doped InP shell compensates for the built-in potential and donates free holes to the InAs core. The effect of shielding critically depends on the thickness of the InP capping layer and the dopant concentration in the shell. [7]

# I.I.4. Si integration

### Al as catalyst for Si nanowires (MPI)

Replacement of Au by other catalysts was one of the main efforts of this work. The metal Al was successfully used as a catalyst at low growth temperature in the VSS mode for growth of freestanding Si nanowires. The template-assisted growth using AAO and Al catalyst allowed to grow (100) oriented Si nanowires. [8]

Fig 9. Si nanowires grown by use of a Al catalyst.

**Epitaxial growth of III-V NWs on Si and Ge (PRE)** The growth of GaAs, GaP, InAs, and InP nanowires on Si and Ge substrates was investigated extensively, and high-quality epitaxial growth was demonstrated for these materials systems. It was shown that the orientation of the epitaxial nanowires depends on the substrate-wire lattice mismatch. [9]

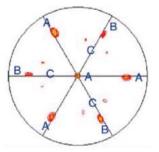

Fig10. X-ray diffraction pole measurements on InP wires grown on Si(111), showing the presence of InP(111) reflections originating from the wires.

### Au-free InAs nanowires on silicon (LU)

Narrow bandgap materials, such as InAs, could have great impact on future nano-electronics if integrated with Si, but integration has so far been hard to realize. InAs nanowires can be grown directly on silicon substrates using a method employing self-assembled organic coatings to create oxide-based growth templates. [10] The method was subsequently modified to also allow for position-control, which is required for vertical device implementation.

Fig 11. Epitaxial InAs nanowires grown on a Si(111) substrate from holes etched in a SiO2 film.

# I.2. Nanoprocessing

# I.2.I. Surface passivation and gate dielectrics

### Lateral nanowire n-MOSFETs (IBM)

Fully depleted lateral n-channel MOSFET devices were fabricated using implantation for source and drain regions. Strong inversion and clear saturation currents are observed in FETs from intrinsic NWs with p-implanted source/drain regions, whereas NWFETs with Schottky contacts only operate in accumulation mode.

The effect of surface preparation on the electrical characteristics were studied and revealed that encapsulating the devices in a protective oxide yields significantly increased on currents and steeper sub-threshold swings. [11] This analysis reveals the strong influence of the electrostatics on the transport properties and shows that the extraction of device parameters using conventional models may not be valid.

Fig 12. Transfer characteristic of a lateral nanowire n-MOSFET as fabricated surrounded by air (black) and encapsulated in SiO\_2.

### Chemical passivation of nanowires (WU)

The large surface to volume ratio of nanowires makes them very sensitive to surface effects such as nonradia-

Fig 13. Photoluminescence spectrum of an as grown (bottom) and a passivated wire (top).

tive recombination centers or trapped charges.

Surface passivation of GaAs nanowires by difference chemical treatments has been investigated and an improvement of the luminescence efficiency by a factor of 40 compared to as-grown wires could be achieved.

# I.2.2. Contacts and gates for nanowire FETs

### 50 nm Lg Wrap Gate InAs MOSFET (QM)

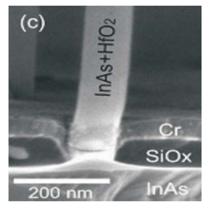

Wrap Gated, or gate all around devices show the best control of the channel potential. InAs high- $\mathcal{K}$  (HfO<sub>2</sub>) oxide nanowire field effect transistor, were successfully fabricated with a 50 nm long wrap gate. The first transistors were based on InAs wires grown on a n+ InAs substrate. The high mobility and injection velocity of the InAs channel leads to a good drive current and excellent transconductance. [12]

Fig 14. Cross section of the MOSFET, showing the 50 nm Cr gate around the  $\ln\!As$  nanowire.

### Schottky barrier FETs (IBM)

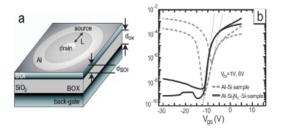

The use of thin  $Si_3N_4$  interface layers between the silicon and metal contacts were shown to give Ohmic contacts whereas without the  $Si_3N_4$  a normal Schottky contact was achieved. Furthermore, it was demonstrated that the  $Si_3N_4$  interface layer gives Schottky barrier FETs with suppressed ambipolar behaviour due to a reduction in metal induced gap states. [13]

Fig 15. Schematic of a Schottky barrier pseudo-MOSFET and the corresponding transfer characteristics with and without an interface layer.

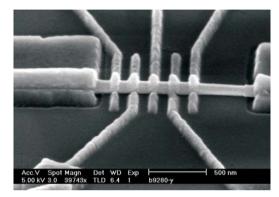

### Multiple gates for nanowire devices (TUD)

Nanowires with multiple gates on horizontal nanowires have been developed to create electrical quantum dots in InAs/ InP nanowires. These devices are used to investigate quantum effects in coupled quantum dots nanowires. [14]

Fig 16. Horizontal InAs/InP nanowire with multiple gates.

# Nanowire FET with gated Schottky contact (WU, NL)

Gated Schottky contacts allow a control over the polarity of the injected carriers, allowing to switch the operation of a nanowire FET from n-type to p-type. Such devices can be used to realize complementary logic without doping the nanowires.

Fig 17. Si-nanowire FET with two gated Schottky contacts.

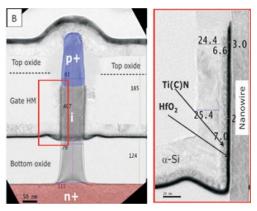

### Wrap-around gate vertical Si nanowire Tunnel-FETs (IMEC)

The NODE project successfully developed a CMOS compatible process flow to fabricate vertical Si nanowire Tunnel-FETs using state-of-the-art processing tools onto 200mm wafers. An advanced gate stack using high- $\kappa$  (HfO<sub>2</sub>) oxide and metal gate (TiN) was implemented.

The top contact was obtained by isotropic dry etch of the gate stack at the top of the wire using a gate hardmask. The gate is isolated from the substrate by a thick oxide layer. It is also isolated from the top contact by a nitride spacer and oxide layer. A capping layer connects multiple wires together. Top contact doping is achieved through epitaxial layer or tilted implants.

Fig 18. Cross section of the vertical TFET featuring 3nm HfO<sub>2</sub>, 7nm TiN and 25nm a-Si gate stack around the nanowires.

### I.2.3. Processing of vertical nanowire devices

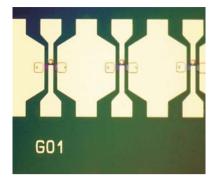

# InAs Wrap Gated MOSFETs for RF and circuit applications (QM/LU)

For RF and circuit applications, the transistors need to be integrated on an highly resistive, or insulating substrate. Technology for growing, and locally contacting InAs nanowires on a semi insulating InP substrate has been developed.

The technology is based on a local ohmic substrate contact, which wraps around the base of the nanowires. This allows for RF characterization of the InAs MOS-FETs, with first results of  $f_t$ =7 GHz and  $f_{max}$ =22 GHz. [15]

Fig 19. Top view of a fully processed RF-compatible vertical nanowire transistor structure.

### Vertical Impact Ionization MOS FETs (IBM-ZRL)

A process for vertical silicon nanowire FETs was developed. Using this process vertical impact ionization FETs with sub-threshold swings down to 5 mV/dec. were demonstrated. [16]

Fig 20. Stability of the transfer characteristics of a vertical IMOS FET.

### Nanowires based spin memory (TUD)

The NODE project created a spin memory in a single quantum dot embedded in an InP nanowire. The preparation of a given spin state by tuning excitation polarization or excitation energy demonstrated the potential of this system to form a quantum interface between photons and electrons.

For this purpose, transparent contacts on vertical nanowires have been developed for FET devices and are currently under investigation. [17]

Fig 21. Vertical nanowire surrounded by a dielectric and a wrap gate.

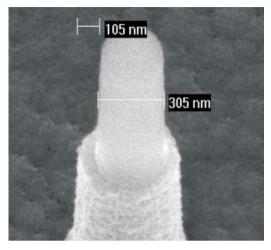

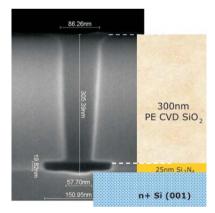

# $SiO_2$ template development for catalyst-free nanowire growth (IMEC)

A process was developed to fabricate hole patterns on top of silicon for constrained growth of Si nanowires, without the use of catalyst. The template was prepared by patterning a plasma–enhanced chemical-vapor deposited (PE CVD) Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> 25nm/300nm film stack

Fig 22. Cross-section of a via hole after plasma etch and hot phosphor opening of the Si\_3N\_4 bottom layer.

with openings or holes to expose the underlying Si. The patterning was performed through 193nm lithography and etching of the SiO<sub>2</sub> with Motif®, an advanced dry etch technique capable of shrinking printed feature sizes thanks to the deposition of a polymeric coating on top of the developed resist. Particular care was dedicated

to cleaning of the side walls and the silicon bottom substrate to avoid defects creation during subsequent growth. To achieve suitable Si purity for epitaxial growth, a special sequence of process steps was needed to avoid Si contamination by carbon residues from etch.

# I.3. Physics and characterization

# **I.3.I. Electrical properties**

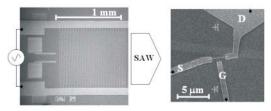

### Room temperature transport (SNS)

Room temperature transport properties of bare InAs and InAs/InP core shell nanowires [18] have been studied and a three dimensional electrostatic model was developed to compute the NW FET capacitance for a more accurate mobility determination. The measured values ranged in the 1-2 thousand  $cm^2/Vs$  for the thinnest wires (< 40 nm), while reached about 3 thousand for thicker wires. Remarkably all the wires showed relatively low values of electronic charge in the few 10<sup>16</sup> cm<sup>-3</sup> range. The highly Se-doped wires revealed an attendant strong increase in charge density up to ~  $1 \times 10^{19}$  cm<sup>-3</sup>; as expected the impurities introduced brought along a decrease in the mobility, which varied in the 4-6 hundred cm<sup>2</sup>/Vs range for wire diameters of 40-50 nm. In parallel, NW devices were fabricated for charge pumping through surface acoustic waves (SAW) [19]. The NW FETs were implemented on top a LiNbO3 substrate with piezoelectric transducers. An acoustoelectric current peak in the wire was identified when driving the transducer near its resonance frequency. This type of devices is quite interesting both for analog signal processing and for the implementation of single-photon sources under quantized charge pumping.

Furthermore, it yields a new direct method to measure the carrier mobility by observing the bias point at which the acoustoelectric peak in the current changes of sign, signaling that drift and acoustic wave velocity are the same.

Fig 23. Sketch of the device and set-up for the induction of acoustoe-lectric current in NW FETs.

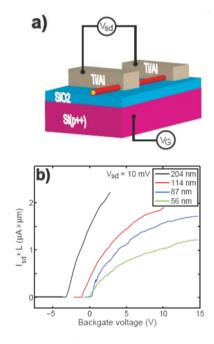

### Diameter dependence of tapered InAs nanowires [20] (TUD, PRE)

Electrical conductance through InAs nanowires is relevant for electronic applications as well as for fundamental quantum experiments. Nominally undoped, slightly tapered InAs nanowires were used to study the diameter dependence of their conductance. Contacting multiple sections of each wire, we can study the diameter dependence within individual wires without the need to compare different nanowire batches. At room temperature we find a diameter-independent conductivity for diameters larger than 40nm, indicative of three-dimensional diffusive transport.

For smaller diameters, the resistance increases considerably, in coincidence with a strong suppression of the mobility. From an analysis of the effective charge carrier density, we find indications for a surface accumulation layer.

Fig 24. (a) The backgate sweeps for different sections within the same nanowire. The inset shows the data for the section with the smallest diameter. (b) The mobility determined from backgate sweeps. Different symbols correspond to the different devices studied.

# Surface passivation of InAs nanowires by an ultrathin InP shell [21] (TUD, PRE)

We report the growth and characterization of InAs nanowires capped with a 0.5-1nm epitaxial InP shell. The low temperature field-effect mobility is increased by a factor 2-5 compared to bare InAs nanowires. The highest low temperature peak electron mobilities obtained for nanowires to this date, exceeding 20 000 cm<sup>2</sup>/Vs we also reported.

Fig 25. (a) pinch-off curve and (b) extracted field-effect (black) and effective mobilities (blue) of a high mobility core/shell nanowire.

The electron density in the nanowires, determined at zero gate voltage, is reduced by an order of magnitude compared to uncapped InAs nanowires. For smaller diameter nanowires, an increase in electron density was found which can be related to the presence of an accumulation layer at the InAs/InP interface. However, compared to the surface accumulation layer in uncapped InAs, this electron density is much reduced.

We suggest that the increase in the observed field-effect mobility can be attributed to an increase of conduction through the inner part of the nanowire and a reduction of the contribution of electrons from the low mobility accumulation layer. Furthermore it was found that by growing an InP shell around an InAs core, surface roughness scattering and ionized impurity scattering in the accumulation layer is reduced.

### **I.3.2. Optical studies**

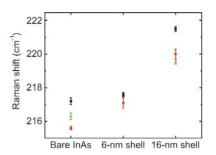

### Raman and mid-IR spectroscopy (SNS)

A micro-Raman set-up was developed and applied to InAs/InP core-shell structure, as a way to study the strain introduced in the structure and verify the reduced impact of surface states in the capped wires. A clear line width reduction was observed in wires with thick InP shells where less interaction with the surface was expected and a blue shift of the resonances with increasing shell thickness was also detected, which gives indication of the amount of strain in the InAs material.

Fig 26. Energy position of the main transverse mode for NWs with different InP shells. Colours are used to distinguish among different wires in the same sample.

# Micro photoluminescence studies of single InP nanowires (WU)

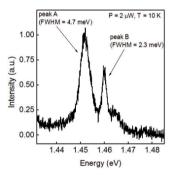

The optical study of single nanowires provides important information about physical properties such as size quantization effects. Individual NWs show narrow emission lines with linewidths as low as 2.3 meV which reflects the high structural quality of the nanowires. Blueshifts of the NW emission energy between 25 and 56 meV with respect to bulk InP are related to radial carrier confinement in nanowires with diameters between 15 nm and 50 nm. Time resolved investigations reveal a low surface recombination velocity of 6×10<sup>2</sup> cm/s. [22]

Fig 27. Micro photoluminescence spectrum showing emission from two InP nanowires with narrow linewidths of 4.7 meV and 2.3 meV, respectively.

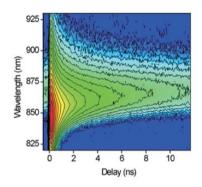

# Study of surface capping of InP nanowires (WU, LU, QM)

Time resolved photo-luminescence spectroscopy was applied to optimize the atomic layer deposition (ALD) of high- $\kappa$  dielectrics (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>) onto InP NWs – a process which typically leads to detrimental surface states. Applying a core/shell growth technique the InP surface quality could be significantly improved in terms of the surface recombination velocity S0 which was redu-

ced to  $SO = 9.0 \times 10^3$  cm/s in comparison with  $SO = 1.5 \times 10^4$  cm/s obtained for an untreated reference sample without surface treatment prior to ALD. In an alternative approach, in-situ post-growth annealing in H<sub>2</sub>S atmosphere prior to ALD resulted in a nearly fourfold decrease of S<sub>0</sub>. These results clearly show the importance of a proper surface treatment prior to oxide capping of III/V NWs for transistor applications.

Fig 28. Spectrally and temporally resolved intensity map of the PL emission from  $HfO_2$  capped InP NWs.

### I.3.3. X-ray characterization

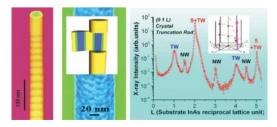

### Study of radial and longitudinal heterostructures (CEA, LU, QuMat)

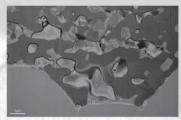

Quantitative structural information about epitaxial arrays of VLS-NWs have been reported for a InAs/InP longitudinal [23] and core-shell [24] heterostructure grown InAs (111)B substrates. Grazing incidence X-ray diffraction allows the separation of the nanowire contribution from the substrate overgrowth and gives averaged information about crystallographic phases, stacking defects, epitaxial relationships with orientation distributions, and strain. The strain profiles have been

Fig 28. Longitudinal and radial heterostructures measured by Grazing Incidence X-ray Techniques and example of a truncation rod measurement showing the [111] stacking in a longitudinal InAs/InP heterostructure.

# International Congress on Nanotechnology and Research Infrastructures Barcelona 26 - 28 May 2010

# The Mission of GENNESYS

Establishing a strategic partnership between nanomaterials research laboratories, universities, industry and the European Research Infrastructures for the advancement of nanomaterials science and technology.

# The Programme includes:

Nanotechnology and Research Infrastructures: European and Global Views

**Challenges in Nanomaterials Design**

The Role of Research Infrastructures for the Advancement of Nanotechnologies Science and Technology Industry Challenges in the World of Open Innovation

Societal Implications of Nanotechnology

Future European and International Needs and Action Plans

# For further information, please visit the website http://www.gennesys2010.eu

compared to atomistic and finite element calculations performed at CEA, and Grazing Incidence Small Angles Scattering has been used to extract the shape, diameter and variability of the NWs.

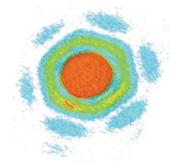

### Single object studies (CEA)

The measurement of single NWs with coherent imaging techniques has been developed. This new technique gains insights into the shape of the objects [25], but also into the strain distribution inside one object. Original structural results obtained on sSOI lines with micro-focussed beams have been obtained (unpublished results) as well as the application of this technique to VLS grown samples.

Fig 29. Coherent diffraction of single 95 nm Si nanowire (111) Bragg reflection. The "ab initio" analysis of this pattern allows reconstructing the shape of the NW.

### I.3.4. Modelling

### Band structure calculations (CEA, LU).

The band structure of group IV and various III-V NWs has actually been investigated in the whole 2-40 nm diameter range. The size dependence of the bandgap energy, subband splittings and effective masses has been discussed in detail [26] and used in collaboration with Lund for the modelling of InAs NW field-effect transistors. [27] Finally, the CEA has investigated the effects of strains on the electronic properties of III-V nanowire heterostructures (e.g., the reduction of the barrier height in tunnel devices). [28]

### **Transport properties (CEA)**

The transport properties of ultimate silicon nanowires with diameters <6 nm has been modeled using quantum Kubo-Greenwood and Green function methods. The impact of surface roughness [29] and dopant impurities on the mobility has been studied. The CEA has shown, in particular, that the impurity-limited contribution to the mobility could be larger in wrap-gate nanowires than in bulk due to the efficient screening of ionized impurities by the gate. Also, the resistance of single impurities can be very dependent on their radial position in the nanowire, leading to significant variability in ultimate devices.

# Effect of dielectric environment on the electrical properties (CEA, CNRS/IEMN, LU)

It was shown that the dielectric confinement can be responsible for a significant decrease of the doping efficiency in nanowires. [30] Dopant impurities are progressively "unscreened" by image charge effects when reducing wire diameter, which leads to an increase of their binding energies and decrease of their activity. These predictions have been confirmed by recent experiments by the IBM group. The binding energies of shallow impurities are however very sensitive to the dielectric environment of the nanowires, and can be decreased by embedding the wires in high-k oxides or wrap-gates. Modelling has confirmed that many electronic properties of semiconductor nanowires are driven more by dielectric than quantum confinement, even in the sub 10 nm range, showing the importance of the "electrostatic" engineering of nanowire devices.

Fig 30. Binding energy of various donors (black symbols, left axis) as a function of the radius R of silicon NWs in vacuum, and room temperature doping efficiency of P donors (red symbols, right axis). The doping efficiency rapidly decreases below R = 10 nm.

### I.4. Nanowire devices

### I.4.I. InAs FETs

### Vertical InAs transistors (LU/QM)

Fabrication of vertical InAs nanowire wrap-gate field- effect transistor arrays with a gate length of 50 nm has been developed. [31] The wrap gate is defined by evaporation of 50-nm Cr onto a 10-nm-thick HfO<sub>2</sub> gate die-

lectric, where the gate is also separated from the source contact with a 100-nm SiO<sub>X</sub> spacer layer. For a drain voltage of 0.5 V, a normalized transconductance of 0.5 S/mm, a subthreshold slope around 90 mV/dec., and a threshold voltage just above 0 V were observed.

Fig 31. Sub-threshold I-V characteristics of an array of 55 vertical InAs nanowires.

# RF characterization of vertical InAs transistors (LU/ QM)

Lund and Qimonda have developed an RF compatible vertical InAs nanowire process, with InAs wires grown on S.I. InP substrates. By combining 70 wires in parallel in a 50 $\Omega$  waveguide pad geometry, S-parameters (50MHz-20 GHz) for vertical InAs nanowire MOSFETs were measured. A maximum ft of 7GHz and fmax=22GHz [32] was obtained. Small signal modelling allowed for the first extraction of intrinsic device elements forming a hybrid- $\pi$  equivalent circuit.

Fig 32. Measured and modelled RF gains for a 90 nm gate length InAs MOSFET.

### I.4.2. Other InAs- and III/V-based devices

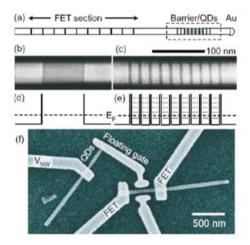

### Nanowire-based multiple quantum dot memory (LU)

We demonstrate an alternative memory concept in which a storage island is connected to a nanowire containing a stack of nine InAs quantum dots, each separated by thin InP tunnel barriers. [33] Transport through the quantum dot structure is suppressed for a particular biasing window due to misalignment of the energy levels. This leads to hysteresis in the charging & discharging of the storage island.

The memory operates for temperatures up to around 150 K and has write times down to at least 15 ns. A comparison is made to a nanowire memory based on a single, thick InP barrier.

Fig 33. Design and implementation of a multiple quantum dot memory based on nanowires.

### Nanowire capacitors (LU)

Vertical InAs nanowire capacitors have been developed based on arrays of nanowires, high-k deposition, and metal deposition. [34] The capacitors show a large modulation of the capacitance with the gate bias, and a limited hysteresis at 0.5 V voltage swing. Via modeling of the charge distribution in the nanowires as a function of the applied voltage, the regions of accumulation, depletion, and inversion have been identified. Finally, the carrier concentration has been determined.

### I.4.3. Si FETs

### Doping limits in silicon nanowires (IBM)

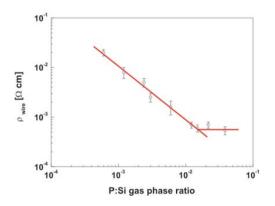

The control over doping levels was demonstrated for insitu doped silicon nanowires using phosphine as the doping source. It was found that the maximum attainable doping is  $1 \times 10^{20}$  cm<sup>-3</sup> limited by the solid solubility limit of phosphorous in silicon at the growth temperature (450°C). [35]

Fig 35. How the resistivity of silicon nanowires increases with decreasing diameter due to doping deactivation caused by a dielectric mismatch between the nanowire core and the surroundings.

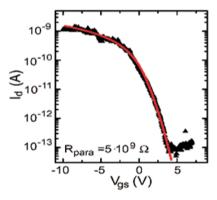

### Silicon nanowire tunnel FETs (IBM)

Tunnel FETs based on silicon nanowires were demonstrated for the first time. The FET structure was grown by the VLS method and doping was incorporated in-situ. The devices were fabricated in a lateral fashion with both a top and bottom gate. The data obtained on the FETs matched the expected sub-threshold slopes as modeled by a simple WKB approximation. [37]

Fig 34. Experimental data of nanowire resistivity vs phosphine concentration. Donor densities up to the solid solubility limit of phosphorous in silicon was achieved.

### Doping deactivation (IBM)

It was demonstrated experimentally that dopants inside scaled semiconductors experience a smaller screening as a function of decreasing size leading to a deactivation of the dopants. This effect is caused by a dielectric mismatch between the semiconductor and the surrounding medium. [36]

Fig 36. Transfer characteristics of a Si NW tunnel FET with top gate. The red line is calculated using the WKB approximation.

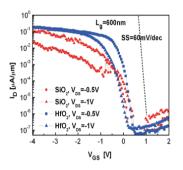

### State-of-the-art all-silicon tunnel FETs (IBM)

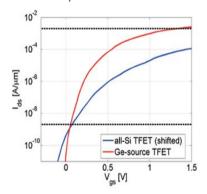

All-silicon nanowire tunnel FETs with high on-currents were demonstrated. The use of a high-k gate dielectric markedly improves the TFET performance in terms of average slope SS (SS measured between  $10^{-7}\mu A/\mu m$  and  $10^{-3}\mu A/\mu m$  is 120 mV/ dec.) and on-current,  $I_{on}(0.3\mu A/\mu m)$ . The performance of the devices is close to what can be expected from all-silicon tunnel FETs. [38]

# Scientific Instruments

www.ioner.eu

# **HV** sources

# Senoidal HV source (HV-7030)

Ramem, SA. C/ Sambara 33 28027 Madrid (Spain) Tel: +34 91 404 45 75 Fax: +34 91 403 45 96 www.ioner.eu ioner@ioner.net

Fig 37. Transfer characteristics of silicon nanowire tunnel FETs with SiO $_2$  (red) and HfO $_2$  (blue) gate dielectrics.

### Dopant-free polarity control of Si nanowire Schottky FETs (NL)

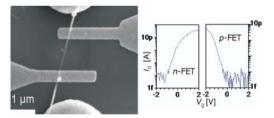

The accurate and reproducible adjustment of the charge carrier concentration in nanometer-scale semiconductors is challenging. As an alternative to transistors containing doping profiles, dopant-free nanowire transistors have been devised. The source and drain regions are replaced by metal contacts that exhibit a sharp interface to the active region. The current flow is controlled by locally adjusting the electric field at the metal/silicon interface. Independent control of each contact results in transistors that can operate either as p- or n-type. [39]

Fig 38. Silicon nanowire FET with two independent top gates, each coupling to a metal/semiconductor junction. The FET can be programmed as p- and n- type.

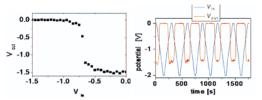

### Complementary logic circuits built from undoped Si nanowire Schottky FETs (NL)

To reduce the static power consumption of digital circuits complementary logic is required. This is enabled by the interconnection between p- and n- type transistors. Complementary nanowire based inverter circuits that do not require doping were developed and characterized. The results show that all logic functions can be performed at low power consumption without dopants. The entire thermal budget for processing is kept below 400°C, enabling a possible future replacement of low mobility organic printed circuits on flexible electronics.

Fig 39. Silicon nanowire inverter characteristics; top: transfer characteristics, bottom: time resolved response.

### **I.5. Benchmarking and integration**

# **I.5.I. Process upscaling of nanowire growth** and devices

### Wafer-scale nanowire growth (IMEC)

At first, catalyst-based growth of silicon vertical nanowire using none-gold catalyst systems was considered. Aluminum, which had been shown promising on coupon level tests (UHV-CVD at MPI), proved not up-scalable in the absence of UHV conditions. Indium particles did produce high-yield Si nanowires in PE-CVD but the growth was difficult to control. In view of the many limitations related to Vapor-Solid Liquid growth of silicon nanowires, a seedless (catalyst-free) constrained approach for growing Si and SiGe nanowires onto Si (100) substrates was developed. The growth approach takes advantage of the advances in Selective Epitaxial Growth (SEG) technology to fill the holes without the presence of catalytic metal particles. Nanowires with an intrinsic

Fig 40. TEM micrograph of a 60nm wide Si/SiGe heterojunction nanowire.

Si segment (channel) and  $p^+$ -doped (B) segment of either Si, Si\_{0.85}Ge\_{0.15} or Si\_{0.75}Ge\_{0.25} (source) were successfully grown on top of n+-doped (100) substrates. [40]

**Large-scale nanowire device integration (IMEC)** IMEC developed an integration flow together with the necessary process modules to fabricate vertical nanowire tunnel-FET devices with wrap-around gates. The nanowires were made by a top-down etch process, however, the integration flow is compatible with a bottom-up approach based on grown nanowires.

Next to the wrap-around gate configuration which provides the best gate control over the channel, a vertical TFET architecture allows a more readily implementation of heterostructures which are needed to boost the tunneling current (see modeling part).

Functional vertical nanowire TFET devices were built on a 200mm wafer platform. [41] Vertical integration implied, among other, the implementation of bottom

# Ni silicide 35nm α-Si Cap layer Nitride spacer 35nm Gate HM 40nm Gate stack HDP oxide 100 nm

Fig 41. TEM cross-section of the final vertical 35nm NW TFET device (no top oxide isolation) with an advanced a-Si/TiN/HfO<sub>2</sub> gate stack

and top isolation layers, and a amorphous Si capping layer which simultaneously connects the TiN metal gate.

# Interest of the second second

# Advertisement

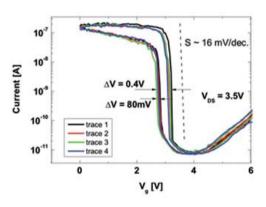

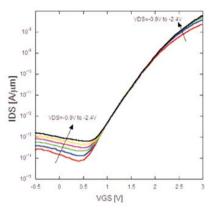

### Vertical nanowire TFET device (IMEC)

Functional Si nanowire n- and p-TFETs were demonstrated and measured electrically at IMEC using a Kleindiek nanoprober apparatus mounted in a HRSEM. The experimental data are inline with literature data of all-Si Tunnel-FETs. To contributors knowledge, these devices are the first large-scale integrated vertical nanowire devices with state-of-the art high-k metal gate stack. [42]

Fig 42. Input  $I_{dr}V_{ge}$  characteristics of the n- TFET device with an epi grown P<sup>+</sup>source and a nanowire size of 50 nm on design.

# I.5.2. Vertical device architectures and benchmarking

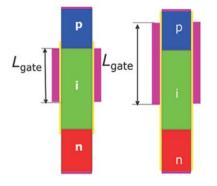

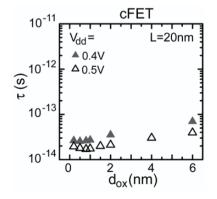

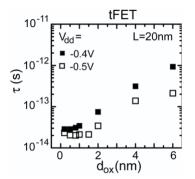

# Short-gate and shifted-gate TFET device concepts (IMEC)

It was shown with the help of simulation that the position of the gate can impact the TFET device performance. The advantage of the short-gate TFET are the

Fig 43. Schematic representation of the short-gate (left) and shifted-gate (right) concepts.

reduced ambipolar behavior, enhanced switching speed and relaxed processing requirements. [43] When the gate is shifted towards the source-channel a modest increase in on-current can be achieved.

### Heterojunction-source TFET (IMEC)

It was shown that the on-current of the TFET device can be increased considerably by placing a foreign source material on top of the Si nanowire channel. Germanium and InGaAs were identified as the source materials of choice for an n-type and p-type TFET device, respectively. The advantage of remaining the Si channel is obvious as conventional Si processing can be used for the gate-stack fabrication. For this work new models needed developed commercial device simulators failed to correctly predict the performance of heterostructure TFETs. [44, 45] Together, the Ge-source for n-type and InGaAs source for p-type, enable a complementary silicon-based TFET suitable for competitive low-power applications. These heterostructure TFET configurations (Ge-Si, InA-Si and In0.6Ga0.4As-Si) and their corresponding I-V characteristics have been used as input for the circuit simulations by NXP.

Fig 44. Comparison of  $I_{\rm ds}-V_{\rm gs}$  characteristics of all-Si TFET (short gate) and the proposed heterostructure Ge-source Si-TFET, indicating the boost of the current with nearly 2 orders of magnitude to the same level as Si MOSFETs (dashed curves).

# I.5.3. Nanowire MOSFETs in the quantum capacitance limit

# Quantum capacitance limit for conventional FETs (IBM)

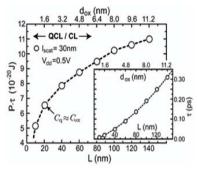

Scaling of NW transistors was investigated by modeling. The important implication of the analysis is that NW with very small diameter enable ultimately scaled transistor devices in a wrap-gate architecture since electrostatic integrity is preserved down to smallest dimensions. However, besides this pure geometrical ar-

Fig 45. Power delay product and gate delay (inset) versus gate length and oxide thickness for conventional FETs as the transition from classical limit to the quantum capacitance limit is made.

gument the present study shows that NWs offer an additional scaling benefit. In the case of 1D transport, devices can be scaled towards the Quantum Capacitance Limit (QCL) which shows a clear scaling advantage in terms of the power delay product, i.e. the energy needed for switching the transistors. As a result, NWs exhibiting 1D transport are a premier choice as channel material for high performance, ultimately scaled FET devices. [46]

### Tunnel FETs in the quantum capacitance limit

Nanowire tunnel FETs versus nanowire MOSFETs (IBM). Modeling of nanowire MOSFETs and tunnel FETs using non-equilibrium Greens functions was used to calculate gate delays as a function of scaling oxide thickness. It was demonstrated that when FETs are scaled to the quantum capacitance limit the tunnel FETs exhibit the same on-state performance as MOSFETs using the gate delay as the performance metric. The on-current is an order of magnitude lower for the TFETs though.

Fig 46. Gate delay versus oxide thickness for nanowire MOSFETs and tunnel FETs.

### References

- [1] P. Caroff et al. Nature Nanotech. 4, 50 (2009)

- [2] R.E. Algra, et al., Nature 456, 369 (2008)

- [3] M.T. Borgström et al., Nature Nanotech. 2, 541 (2007)

- [4] T. Shimizu et al., Nano Lett. 9, 1523 (2009)

- [5] K.A. Dick et al. Nano Lett. 7, 1817 (2007)

- [6] E.D. Minot et al. Nano Lett. 7, 367 (2007)

- [7] H.-Y. Li et al,. Nano Lett. 7, 1144 (2007)

[8] Y.W. Wang et al., Nature Nanotech., I, 186 (2006); Z. Zhang et al., Adv. Mater.

- [9] E.P.A.M. Bakkers et al., MRS Bulletin 32, 117 (2007)

- [10] T. Mårtensson et al. Adv. Mat. 19, 1801, (2007)

- [11] O. Hayden et al., Small, 3, p. 230, 2007

- [12] C. Thelander et al. IEEE Electron Device Lett. 2008

- [13] H. Ghoneim et al., Proceedings of ULIS conference 2009

- [14] M. Scheffler et al., Physica E 40, 12020-01204 (2008)

- [15] M. Egard et al. submitted to Nano Lett. 2009

- [16] M. T. Björk et al., Appl. Phys. Lett. 90, 142110 (2007)

- [17] H.M. Maarten et al., Small 5, pp. 2134 2138 (2009)

- [18] S. Roddaro et al., Nanotechnology 20, 285303 (2009)

- [19] S. Roddaro et al., submitted to Semicond. Science Tech.

- [20] M. Scheffler et al., submitted to Journal of Applied Physics

$\left[ 21\right]$  J. van Tilburg et al., accepted for publication in Semiconductor Science and Technology

- [22] S. Reitzenstein et al., Appl. Phys. Lett. 91, 091103 (2007)

- [23] J. Eymery et al., Nano Letters 7 (9) 2596 (2007)

- [24] J. Eymery et al., Appl. Phys. Lett. 94, 131911 (2009)

- [25] V. Favre-Nicolin et al., Phys. Rev. B 79, 195401 (2009)

- [26] Y. M. Niquet et al., Phys. Rev. B 73, 165319 (2006)

- [27] E. Lind et al., IEEE Trans. Electron Devices 56, 201 (2009)

- [28] Y. M. Niquet and D. Camacho Mojica, Phys. Rev. B 77, 115316 (2008)

- [29] M. P. Persson et al., Nano Letters 8, 4146 (2008)

- [30] M. Diarra et al., Phys. Rev. B 75, 045301 (2007)

- [31] C. Thelander et al. IEEE Electron Dev. Lett. 29, 206 (2008)

- [32] M. Egard et al., submitted to Nano Lett.

- [33] H. N. Nilsson et al. Appl. Phys. Lett 89, 163101 (2006)

- [34] S. Roddaro et al. Appl. Phys.Lett. 92, 253509 (2008)

- [35] H. Schmid et al., Nano Lett. 9, 173 (2009).

- [36] M. T. Björk et al., Nature Nanotechn. 4, 103 (2009)

- [37] M. T. Björk et al., Appl. Phys. Lett. 92, 193504 (2008)

- [38] K. E. Moselund et al., ESSDERC, September 2009

- [39] W. M. Weber et al. IEEE Proc. Nanotech. Conf. p.580 (2008)

- [40] F. Iacopi et.al., MRS Symposium Proceedings, Vol. 1178E

- [41] A. Vandooren et al., Proc. Silicon Nanoelectronic Workshop, pp. 21-22, Kyoto, June 2009

- [42] D. Leonelli et al., submitted to Electron Device Letters

- [43] A.S. Verhulst et al., Appl. Phys. Lett. 91, 53102 (2007)

- [44] A.S. Verhulst et al., J. Appl. Phys. 104, 64514 (2008)

- [45] A.S. Verhulst et al., Electron Dev. Lett. 29, 1398 (2008)

- [46] J. Appenzeller et al., IEEE Trans. Electron. Dev. Vol. 55, pp. 2827-2845, (2008)

### 2. Overview of nanowire growth

Nanowires can be grown by a variety of methods, but the most common method by far is particle-assisted growth [1, 2] in metal-organic vapor phase epitaxy (MOVPE) or molecular beam epitaxy. This technique uses metal seed particles, most often gold, which act as nucleation centers [3] and direct the growth. The size, number and position of the resulting nanowires are determined by the seed particles, potentially allowing for a high degree of control over the final structures. In this section, patterned growth, heterostructures, doping, crystal structure control, and metal free growth will be briefly reviewed.

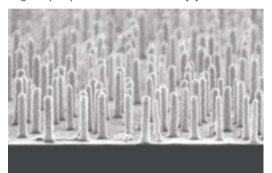

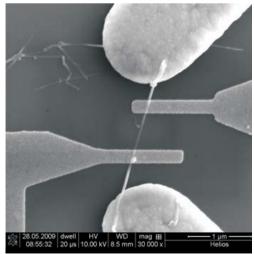

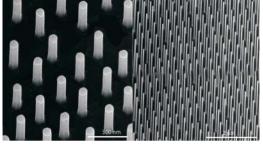

The gold seed particles can be deposited in a few different ways. Deposition of aerosol or colloid particles results in more or less randomly positioned nanowires. However, most applications require precise control of the nanowires, both in terms of position and size. Defining the gold particles by electron beam lithography, followed by gold evaporation and lift off, allows for this [4], see Fig. 1.

Formation of heterostructures is at the core of nanowire technology and novel device structures. Three major categories can be identified: axial, radial, and substrate/nanowire heterostructures, e. g. III–V nanowires on Si substrates.

First, axial structures can be formed if the growth precursors are alternated during growth. This results in a variation of the composition along the wire. Furthermore, it is well understood that nanowires represent an ideal system for the growth of axial heterostructures, since mismatched materials can be grown epitaxially on each other without misfit dislocations. This is possible because strain can be relieved by coherent expansion of the lattice outwards (along the wire diameter), avoiding dislocations. Axial heterostructure nanowires were first demonstrated in 1994 for the GaAs-InAs system [5]. Further development of this material system led to reports of high-quality interfaces despite the large lattice mismatch [6]. For the InAs–InP system, atomically sharp interfaces were also reported [7]. Nanowire heterostructure superlattices have been demonstrated for a variety of material systems, with lattice mismatch as high as 3% [8]. Much recent work has focused on attaining sharp heterointerfaces for various material and growth systems. As well, the development of heterostructure nanowires involving ternary compounds such as GaAsP [9], InAsP [10] and InGaAs [11], further increases the potential for applications.

Second, radial structures, also known as core-shell structures, can be formed. In the lateral case, heterostructures are achieved by first growing nanowires by conventional particle-assisted growth, then by changing the growth parameters so that bulk growth is favored. In this way growth on the side facets of the wire will dominate, and shells will form [12].

Fig 1. Scanning electron micrographs of gold particle-assisted, MOVPE grown, InAs nanowires in regular arrays, where the positions of the gold particles have been defined by electron beam lithography.

The third category, substrate/nanowire heterostructures, resembles the axial heterostructure with the difference that the substrate is less compliant. Compared to planar heteroepitaxy, the critical thickness for dislocation-free growth becomes considerable larger when strain can be relaxed also radially. This effect enables epitaxy of III–V nanowires on Si [13].

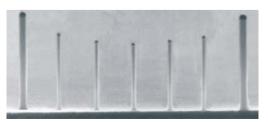

Fig 2. Transmission electron micrograph of a ZB-WZ polytypic superlattice in an InAs nanowire. The structure was achieved by periodically varying the growth temperature.

# Advertisement

For electronics and optoelectronics applications it is necessary to control the conductivity and to be able to fabricate pn-junctions in nanowires. Thus it is of high importance to be able to dope the nanowires; pn-junctions in nanowires have been reported for nitride [14] and other III–V [15, 16] nanowires, even though the incorporation mechanism during particle-assisted growth is not well understood.

Semiconductor nanowires composed of III-V materials such as InAs typically suffer from frequent stacking defects. Although most of these materials exhibit zinc blende (ZB) structure in bulk, nanowires may also be composed of the related wurtzite (WZ) structure. If nanowire growth is not carefully controlled, the resulting structure may consist of a mixture of these two phases, together with twin planes, stacking faults and other polytypes. Various theoretical and experimental works have indicated that uncontrolled structural mixing may be detrimental to electronic and optical properties, and structural variations due to random intermixing may lead to unacceptable variability in material properties. On the other hand, the ability to select between ZB and WZ and to mix these structures in a controlled way may give access to new and exciting physics and applications.

It has recently been shown that the crystal structure of InAs nanowires can be tuned between pure WZ and pure ZB by careful control of experimental parameters, where temperature and nanowire diameter are the most significant [17]. This knowledge enabled the fabrication of twin plane superlattices and ZB-WZ polytypic superlattices in nanowires, see Fig. 2. Twin plane superlattices has also been controllably produced in InP nanowires by the introduction of dopants [18].

Finally, a successful method to grow perfect ZB nanowires that has been reported for GaAs nanowires is to use a two temperature method, where the growth is initiated at high temperature. After this, the temperature is decreased and the main parts of the nanowires are grown at a lower temperature in order to not overcome the energy barrier for twin formation [19]. Quite surprisingly, the same group has recently reported that nanowires free from planar defects can be achieved by growth at high rate [20].

If semiconductor nanowires will be integrated in CMOS compatible processes, as suggested as one possible path to continue the downscaling of electronics, it is necessary to avoid growth from gold particles. Either, other more CMOS compatible metals have to be utilized as seed particles, or particle free nanowire growth has to

be relized. Particle free growth from mask openings has been realized in InP [21], GaAs [22], and GaN [23]. Metal free growth has also been realized by growth from self-assembled nucleation templates on organically coated surfaces [24].

### References

[1] K. A. Dick, Prog. Cryst. Growth Charact. Mater. 54 (2008) 138

[2] K. W. Kolasinski, Curr. Opin. Solid State Mater. Sci. 10 (2006) 182

[3] B. A. Wacaser, K. A. Dick, J. Johansson, M. T. Borgström, K. Deppert, and L. Samuelson, Adv. Mater. 21 (2009) 153

[4] H. J. Fan, P. Werner, and M. Zacharias, Small 2 (2006) 700

[5] K. Hiruma, H. Murakoshi, M. Yazawa, K. Ogawa, S. Fukuhara, M. Shirai, and T. Katsuyama, IEEE Trans. Electron. E77 (1994) 1420

[6] B. J. Ohlsson, M. T. Bjork, A. I. Persson, C. Thelander, L. R. Wallenberg, M. H. Magnusson, K. Deppert, and L. Samuelson, Physica E 13 (2002) 1126

[7] M. T. Bjork, B. J. Ohlsson, T. Sass, A. I. Persson, C. Thelander, M. H. Magnusson, K. Deppert, L. R. Wallenberg, and L. Samuelson, Nano Lett. 2 (2002) 87

[8] M. S. Gudiksen, L. J. Lauhon, J. Wang, D. C. Smith, and C. M. Lieber, Nature 415 (2002) 617

[9] C. P. T. Svensson, W. Seifert, M. W. Larsson, L. R. Wallenberg, J. Stangl, G. Bauer, and L. Samuelson, Nanotechnology 16 (2005) 936

[10] A. I. Persson, M. T. Bjork, S. Jeppesen, J. B. Wagner, L. R. Wallenberg, and L. Samuelson, Nano Lett. 6 (2006) 403

I. Regolin, D. Sudfeld, S. Luttjohann, V. Khorenko,

W. Prost, J. Kastner, G. Dumpich, C. Meier, A. Lorke,

and F. J. Tegude, J. Cryst. Growth 298 (2007) 607

[12] Y. Li, F. Qian, J. Xiang, and C. M. Lieber, Mater. Today 9 (2006) 18

[13] K. A. Dick, K. Deppert, L. Samuelson, L. R. Wallenberg, and F. M. Ross, Nano Lett. 8 (2008) 4087 [14] H. M. Kim, Y. H. Cho, H. Lee, S. I. Kim, S. R. Ryu, D. Y. Kim, T. W. Kang, and K. S. Chung, Nano Lett. 4 (2004) 1059

[15] E. D. Minot, F. Kelkensberg, M. van Kouwen, J. A. van Dam, L. P. Kouwenhoven, V. Zwiller, M. T. Borgstrom, O. Wunnicke, M. A. Verheijen, and E. P. A. M. Bakkers, Nano Lett. 7 (2007) 367

[16] M. T. Borgstrom, E. Norberg, P. Wickert, H. A. Nilsson, J. Tragardh, K. A. Dick, G. Statkute, P. Ramvall, K. Deppert, and L. Samuelson, Nanotechnology 19 (2008) 445602

[17] P. Caroff, K. A. Dick, J. Johansson, M. E. Messing, K. Deppert, and L. Samuelson, Nature Nanotech. 4 (2009) 50

[18] R. E. Algra, M. A. Verheijen, M. T. Borgström, L. F. Feiner, G. Immink, W. J. P. van Enckevort, E. Vlieg, and E. P. A. M. Bakkers, Nature 456 (2008) 369

# nanoICT research

[19] H. J. Joyce, Q. Gao, H. H. Tan, C. Jagadish, Y. Kim, X. Zhang, Y. N. Guo, and J. Zou, Nano Lett. 7 (2007) 921

[20] H. J. Joyce, Q. Gao, H. H. Tan, C. Jagadish, Y. Kim,

M. A. Fickenscher, S. Perera, T. B. Hoang, L. M. Smith,

H. E. Jackson, J. M. Yarrison-Rice, X. Zhang, and J. Zou,

Nano Lett. 9 (2009) 695

[21] P. Mohan, J. Motohisa, and T. Fukui, Nanotechnology 16 (2005) 2903

[22] K. Ikejiri, J. Noborisaka, S. Hara, J. Motohisa, and T. Fukui, J.Cryst. Growth 298 (2007) 616

[23] S. D. Hersee, X. Y. Sun, and X. Wang, Nano Lett. 6 (2006) 1808

[24] T. Mårtensson, J. B. Wagner, E. Hilner, A. Mikkelsen, C. Thelander, J. Stangl, B. J. Ohlsson, A. Gustafsson, E. Lundgren, L. Samuelson, and W. Seifert, Adv. Mater. 19 (2007) 1801

# Advertisement

# 3. Overview transport/optical properties of nanowires<sup>2</sup>

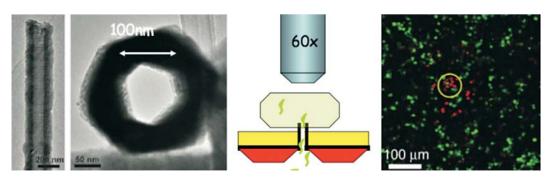

Nanometer-sized quasi 1-dimensional systems, such as semiconducting nanowires (NWs), are attractive building blocks for bottom-up nanotechnology including optoelectronics [1, 2] and manipulation of isolated electron spins [3, 4, 5]. Defect-free nanowire heterojunctions, both longitudinal [6] and radial [7, 8, 9], can be grown due to the small nanowire radius, which allows strain from lattice mismatch to be relaxed radially outwards.

Not only junctions between various different group III-V or IV elements, but even group III-V/IV junctions were reported [10, 11]. InAs is an attractive material because its small bandgap results in a low effective electron mass, giving rise to high bulk electron mobilities (at room temperature 22 700 cm<sup>2</sup>/Vs [12] and at low temperature in planar structures over 600 000 cm<sup>2</sup>/Vs [13]).

For bulk InAs, it is well known that the surface contains a large number of states that lie above the conduction band minimum and can contribute electrons to form a surface accumulation layer with a typical downward band bending between 0 and 0.26 eV [14]. Because of the large surface charge density, the Fermi level for InAs is pinned in the conduction band, which makes it easy to fabricate ohmic contacts without a Schottky barrier.

This InAs contact property enabled the observation of the superconductivity proximity effect in nanowires [15]. A surface accumulation layer combined with the large surface to volume ratio for InAs nanowires could promise good sensitivity for InAs nanowire sensor applications.

As a fraction of the surface states contributes electrons to the accumulation layer, the InAs surface contains a large number of ionized impurities. Electrons in the accumulation layer therefore experience much stronger ionized impurity scattering than electrons in the inner InAs region. Furthermore, because of the proximity to the surface, surface roughness scattering is also strong. This means that electrons in the surface layer have a strongly reduced mobility compared to electrons in the inner material, typically  $\mu$ surface ~ 4000 cm<sup>2</sup>/Vs [12, 14]. For microns thick planar structures of InAs, conduction is dominated by the electrons flowing through the inner region and mobilities are high. The electron mobility is strongly reduced for sub-micron sized InAs structures [12, 14], because of the higher surface-to-bulk ratio. At the same time, the total electron density will increase for smaller thicknesses.

Indications of a surface accumulation layer in InAs nanowires have been observed in [16], where smaller nanowire diameters show an increase in total electron density, consistent with the observations on accumulation layers in bulk InAs [12]. For InN nanowires, magneto-resistance measurements showed Altshuler -Aronov - Spivak (AAS) oscillations, suggestive of shelllike conduction through nanowires [17].

Conduction through InAs nanowires with typical diameters under 200 nm can be expected to be strongly influenced by the presence of a surface accumulation layer. The strong ionized impurity and surface roughness scattering in the surface accumulation layer could explain why InAs nanowires typically have low temperature mobilities of 1000-4000 cm<sup>2</sup>/Vs [15, 18, 19, 20]. There have been two reports of InAs nanowires yielding mobilities exceeding 16000 cm<sup>2</sup>/Vs [21, 22].

The surface band bending that causes the accumulation layer for InAs is a crystal surface property and the strength of the accumulation is known to be dependent on the surface orientation and termination [14]. Reducing the depth of the band bending will result in a higher relative contribution from the inner electrons to the total conduction and an increase in electron mobility.

An alternative approach to increase electron mobility would be to reduce the scattering in the surface channel by reducing the surface roughness and the scattering on surface states by surface passivation. Natural III-V oxides are soft, hygroscopic, compositionally and structurally inhomogeneous [23,24].

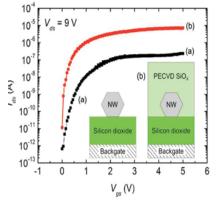

We have extracted the electron mobility from the gate dependence of the current using a simulated nanowire capacitance to the gate. Low temperature mobility has increased by a factor of 2-5 compared to bare InAs nanowires [9]. We also have found among the highest low temperature peak electron mobilities reported to this date, exceeding 25000 cm<sup>2</sup>/Vs.

<sup>30&</sup>lt;sup>2</sup> Val Zwiller, and L P Kouwenhoven

Kavli Institute of Nanoscience, Delft University of Technology, Lorentzweg 1, 2628 CJ Delft, The Netherlands

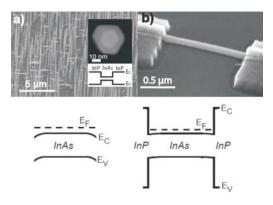

Fig 1. (a) Scanning electron microscope (SEM) image of InAs/InP core/shell nanowires grown on an InP substrate. Inset shows a high angle annular diffraction TEM image of a representative InAs/InP core/shell nanowire. The wire diameter is roughly 20 nm and the shell thickness 7-10 nm. The schematic shows the bandgap alignment for InAs sandwitched between InP. (b) SEM image of a typical nanowire device with Ti/Al contacts as used in our measurements. (c) Schematic of the bandgap bending of an InAs nanowire (a) and an InAs/InP core/shell nanowire.

Fig 2. (a) Schematic of a Ti/AI contacted nanowire on a heavily doped Si substrate with SiO2 dielectric. (b) Current through the nanowire as a function of backgate voltage for several NW diameters. Such measurements are used to determine the electron mobility.

# nanoICT research

To create active photonic elements, the first key step is to incorporate a single quantum dot in a nanowire [25]. Semiconductor quantum dots are well known sources of single [26, 27] and entangled photons [28, 29, 30] and are naturally integrated with modern semiconductor electronics. Incorporation in semiconducting nanowires brings additional unique features such as natural alignment of vertically stacked quantum dots to design quantum dot molecules and an inherent one-dimensional channel for charge carriers. Furthermore, the unprecedented material and design freedom makes them very attractive for novel opto-electronic devices and quantum information processing.

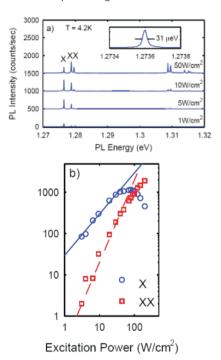

Fig 3. (a) Power dependence of the photoluminescence from a single quantum dot in a nanowire under continuous excitation at 532 nm. (b) Integrated power dependence of two narrow emission lines attributed to the exciton and biexciton. Samples grown by the Bakkers group.

Access to intrinsic spin and polarization properties of a quantum dot in a nanowire is challenging because of the limited quality of nanowire quantum dots, partly because the quantum dot is located very close to the sample surface. Moreover, the nanowire geometry strongly affects the polarization of photons emitted or absorbed by a nanowire quantum dot, and is thus an important obstacle for applications based on intrinsic spin or po-

larization properties of quantum dots such as electron spin memory or generation of entangled photons. It has been shown that photoluminescence of homogeneous nanowires is highly linearly polarized with a polarization direction parallel to the nanowire elongation.

In Fig. 3(a) we show a typical excitation power dependence revealing a usual exciton-biexciton behavior and a p-shell at 30 meV higher energy. The inset shows the narrowest emission we have observed to date with a FWHM of 31  $\mu$ eV, limited by our spectral resolution. The integrated photoluminescence intensities of the exciton and biexciton as a function of excitation power, represented in Fig. 3(b), show that the exciton (biexciton) increases linearly (quadratically) with excitation power and saturates at high excitation powers. This behaviour is typical for the exciton and biexciton under continuous excitation.

The nanowire geometry is not the only source of polarization anisotropy. Calculations by Niquet and Mojica [31] show that the polarization properties are strongly affected by the aspect ratio of the quantum dot dimensions, due to strain originating from the lattice mismatch between the nanowire and the quantum dot. However, in our case the strain is negligible due to the low phosphorus content and the main contribution to polarization anisotropy stems from the nanowire geometry.

Fig 4. (a) and (b) Polarization sensitive photoluminescence of a standing nanowire quantum dot at 9 T. The solid (dashed) curve in (a) represents vertical (horizontal) linearly polarized exciton emission, denoted by H (V). The solid (dashed) curve in (b) represents left- (right-) hand circularly polarized exciton emission. (b) PL of a standing nanowire quantum dot under external magnetic field. Magnetic field is varied between 0 and 9 T in steps of 0.5 T. Sample grown by the Bakkers group (Philips).

Standing nanowires enable the extraction of any polarization with equal probability. This enables the observation of Zeeman splitting, provided that the emission linewidth is narrow enough. In Fig. 4(a) we show a magnetic field dependence of the exciton emission measured on a standing InP nanowire containing an InAsP quantum dot. The nanowire was grown by MOVPE using colloidal gold particles as catalysts by the Bakkers group. Polarization studies at 9 T show circular polarization Fig. 4(b) and no linear polarization Fig 4(a).

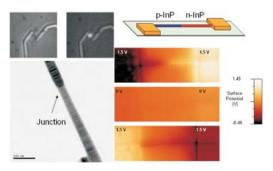

One challenge is to obtain good ohmic contacts to the p doped side of a nanowire LED. In Fig. 5 the device-layout, the nanowire LED emission and the electrostatic potential distribution along the device are shown. The junction is readily visible by transmission electron microscopy, the modification in doping brings about a modification of the nanowire diameter. Electrostatic force measurements are shown on the right of Fig. 5, under a reverse bias of 1.5 V, a prominent drop in potential is observed at the expected position of the pn junciton. Under zero and 1.5 V forward bias, no potential drop is observed on the pn junction, this demonstrates the presence of a pn junction in the contacted nanowire and shows that the contacts are ohmic.

Fig 5. Single nanowire light emitting diode. Left: microscope image of the nanowire LED without and with forward bias. Bottom left: TEM image of a pn junction in an InP nanowire. Right: electrostatic force measurements under forward (top) and reverse (bottom) bias.

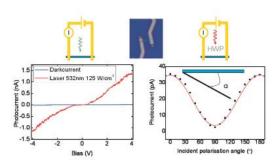

An electrically contacted nanowire can also be used for photodetection, as shown in figure 6. Fig. 6 left shows the photocurrent intensity as a function of applied bias in the dark and under illumination. Fig. 6 right shows the polarization dependence of the photocurrent for a lying nanowire as a function of the laser linear polarization angle. The observed photocurrent polarization is in agreement with the polarization ratio measured by photoluminescence.

Fig 6. Photocurrent measurement on a single nanowire. Left: photocurrent as a function of applied bias. Right: photocurrent as a function of laser polarization.

# References

[1] M. S. Gudiksen, L. J. Lauhon, J. Wang, D. C. Smith, and C. M. Lieber. Growth of nanowire superlattice structures for nanoscale photonics and electronics. Nature, 415:617, 2002

[2] E. D. Minot, F. Kelkensberg, M. van Kouwen, J. A. van Dam, L. P. Kouwenhoven, V. Zwiller, M. T. Borgstrom, O. Wunnicke, M. A. Verheijen, and E. P. A. M. Bakkers. Single quantum dot nanowire LEDs. Appl. Phys. Lett., 7:367, 2007

[3] M. T. Bjork, A. Fuhrer, A. E. Hansen, M. W. Larsson, L. E. Froberg, and L. Samuelson. Tunable effective g factor in InAs nanowire quantum dots. Phys. Rev. B, 72:201307, 2005

[4] A. Pfund, I. Shorubalko, K. Ensslin, and R. Leturcq. Suppression of spin relaxation in an InAs nanowire double quantum dot. Phys. Rev. Lett., 99:036801, 2007

[5] F. A. Zwanenburg, C. E. W. M. van Rijmenam, Y. Fang, C. M. Lieber, and C. M. Kouwenhoven. Spin states in the first four holes in a silicon nanowire quantum dot. Nanoletters, 9:1071, 2009

[6] M. T. Bjork, C. Thelander, A. E. Hansen, L. E. Jensen, M. W. Larsson, L. Reine Wallenberg, and L. Samuelson. Few-electron quantum dots in nanowires. Nanoletters, 4:1621, 2004 [7] W. Lu, J. Xiang, B. P. Timko, Y. Wu, and C.M. Lieber. One-dimensional hole gas in germanium/silicon nanowire heterostructures. PNAS, 102:10046, 2005

[8] H.-Y. Li, O. Wunnicke, M. T. Borgstrom, W. G. G. Immink, M. H. M. van Weert, M. A. Verheijen, and E. P. A. M. Bakkers. Remote p-doping of InAs nanowires. Nanoletters, 7:1144, 2007

[9] X. Jiang, Q. Xiong, S. Nam, F. Qian, Y. Li, and C. M. Lieber. InAs/InP radial nanowire heterostructures as high mobility devices. Nanoletters, 7:3214, 2007

[10] E. P. A. M. Bakkers, J. A. van Dam, S. de Franceschi, L. P. Kouwenhoven, M. Kaiser, M. Verheijen, H. Wondergem, and P. van der Sluis. Epitaxial growth of InP nanowires on germanium. Nature Materials, 3:769, 2004

[11] T. Martensson, C. P. T. Svensson, B. A. Wacaser,

M. W. Larsson, W. Seifert, K. Deppert, A. Gustafsson,

L. R. Wallenberg, and L. Samuelson. Epitaxial III-V nanowires on silicon. Nanoletters, 4:1987, 2004

[12] H. H. Wieder. Transport coefficients of InAs epilayers. Appl. Phys. Lett., 25:206, 1974

[13] S. A. Chalmers, H. Kroemer, and A. C. Gossard. The growth of (Al,Ga)Sb tilted superlattices and their heteroepitaxy with inas to form corrugated-barrier quantum wells. J. Crystal Growth, 111:647, 1991

[14] C. Affentauschegg and H. H. Wieder. Properties of InAs/InAlAs heterostructures. Semiconductor Science and Technology, 16:708, 2001

[15] Y. J. Doh, J. A. van Dam, A. L. Roest, E. P. A. M. Bakkers, L. P. Kouwenhoven, and S. De Franceschi. Tunable supercurrent through semiconductor nanowires. Science, 309:272, 2005

[16] S. A. Dayeh, E. T. Yu, and D. Wang. Transport coefficients of InAs nanowires as a function of diameter. Small, 5:77, 2009

[17] T. Richter, C. Blomers, H. Luth, R. Calarco, M. Indlekofer, M. Marso, and T. Sch apers. Flux quantization effects in InN nanowires. Nanoletters, 8:2834, 2008

[18] T. Bryllert, L. E. Wernersson, L. E. Froberg, and L. Samuelson. Vertical high-mobility wrap-gated InAs nanowire transistor. IEEE Electron Device Letters, 27:323, 2006

[19] A. Pfund, I. Shorubalko, R. Leturcq, F. Borgstrom, M. Gramm, E. Muller, and K. Ensslin. Fabrication of semiconductor nanowires for electronic transport measurements. Chimia, 60:729, 2006

[20] Q. Hang, F. Wang, P. D. Carpenter, D. Zemlyanov, D. Zakharov, E. A. Stach, W. E. Buhro, and D. B. Janes. Role of molecular surface passivation in electrical transport properties of InAs nanowires. Nanoletters, 8:49, 2008

[21] A. C. Ford, J. C. Ho, Y. L. Chueh, Y. C. Tseng, Z. Fan, J. Guo, J. Bokor, and A. Javey. Diameter dependent electron mobility of InAs nanowires. Nanoletters, 9:360, 2009

[22] S. A. Dayeh, C. Soci, P. K. L. Yu, E. Yu, and D. Wang. Transport properties of InAs nanowire field effect transistors: The effects of surface states. Journal of Vacuum Science and Technology B, 25:1432, 2007

[23] H. H. Wieder. Perspective on III-V-compound MIS structures. J. Vac. Sci. Technol., 15:1498, 1978

[24] D. B. Suyatin, C. Thelander, M. T. Bjork, I. Maximov, and L. Samuelson. Sulphur passivation for ohmic contact formation to InAs nanowires. Nanotechnology, 18:105307, 2007

[25] Optically Bright Quantum Dots in Single Nanowires

Borgstrom, M. T.; Zwiller, V.; Muller, E.; Imamoglu,

A.Nano Lett.; (Letter); 2005; 5(7); 1439-1443

[26]A Quantum Dot Single-Photon Turnstile Device, P. Michler, A. Kiraz, C. Becher, W. V. Schoenfeld, P. M. Petroff, Lidong Zhang, E. Hu, A. Imamoglu, Science 22 December 2000, 290, 2282

[27] Single quantum dots emit single photons at a time: Antibunching experiments

Valery Zwiller, Hans Blom, Per Jonsson, Nikolay Panev, Soren Jeppesen, Tedros Tsegaye, Edgard Goobar, Mats-Erik Pistol, Lars Samuelson, Gunnar Bjork, Appl. Phys. Lett 78, 2476 (2001)

[28] Akopian, N., N. H. Lindner, et al. (2006). "Entan-

gled Photon Pairs from Semiconductor Quantum Dots." Physical Review Letters 96(13)

[29] Young, R., M. Stevenson, et al. (2006). "Improved fidelity of triggered entangled photons from single quantum dots." New Journal of Physics 8(2): 29

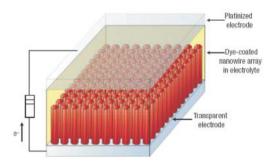

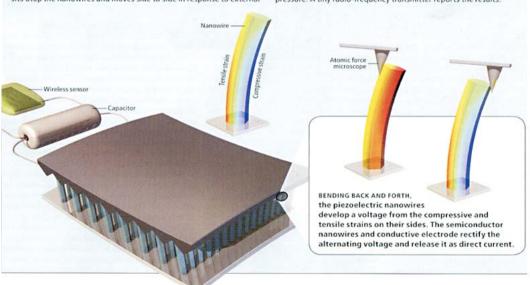

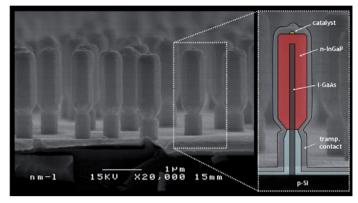

[30] Hafenbrak, R., S. M. Ulrich, et al. (2007). "Triggered polarization-entangled photon pairs from a single quantum dot up to 30K." New J. Phys. 9(9): 315